您好,伟大的英雄,欢迎来到FPGA技术世界。世界是如此之大,会议是命运。英雄们可以关注FPGA技术行业,在“破坏世界”中获得其他有趣的资源,“首席和公义”列,或者一起做饭并玩得开心。

您好,DA Hero,我最近很忙,我没有时间更新。花了很长时间,我担心每个人都会忘记我。今天我在这里。如今,“ 1982年计划元”本扬为基于FIR滤波器带来了白色极限噪声的Daxia设计。 Benyuan将继续在未来的产品项目开发经验,学习经验等中更新,欢迎继续关注,而无需说出很多话,并且可以使用。

1。高斯白噪声

高斯噪声:是一个随机噪声,而时域中信号振幅的统计规则遵守高斯分布。

白噪声:信号的功率谱在整个频域中恒定。

带限制的白色噪声:带宽的高斯白噪声限于一定范围。

2。生成方法

传统高斯白噪声的产生是通过D/A转换器传递多个M序列,然后通过过滤器获得它们,这很麻烦。该项目将通过线性反馈移位寄存器和FIR过滤器来完成。

首先,通过MATLAB中的WGN函数生成高斯白噪声,生成的噪声数据存储在ROM中。然后,M序列伪随机代码是通过LFSR作为ROM地址生成的,以读取噪声数据以增加其随机性。最后,通过用带限制的美白噪声通过FIR过滤获得输出随机噪声。

3。线性反馈移位寄存器(LFSR)

伪随机代码的性能指标直接影响白噪声的随机性。该设计使用Xilinx提供的LFSR IP核心来实现它。

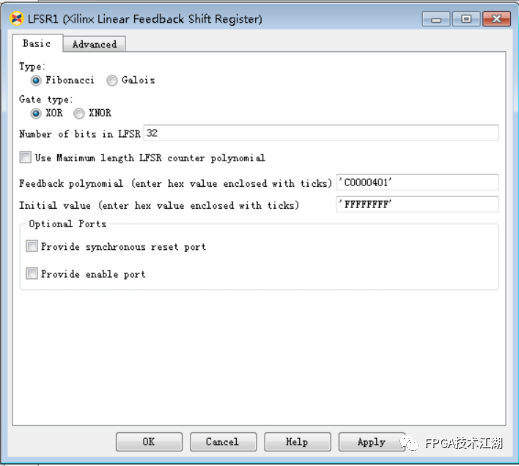

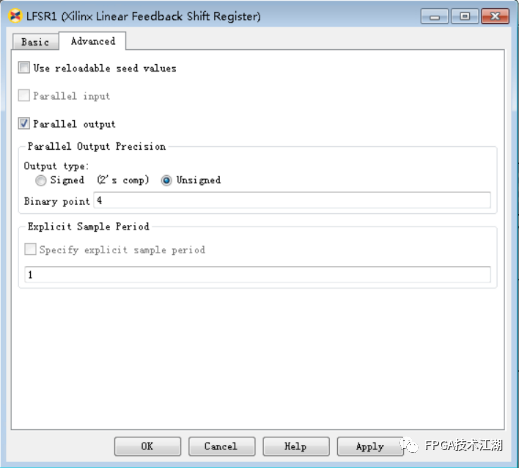

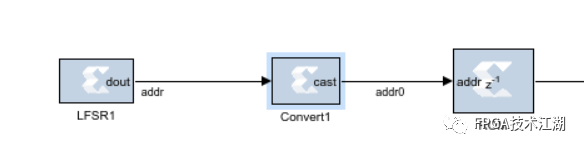

可以如图所示配置LFSR,并且可以选择输出数据类型,位宽度,小数位置等。

此设计将数据类型选择为UFIX_32_4,然后通过转换将其切割为ufix_10_0的数据输出作为ROM地址,这再次改善了随机性。

4。FIR滤波器系数重新加载

过滤器的该部分的设计是在使用可重新加载系数模式下选择的,该模式接收系统发送的滤波器系数,并生成可变带宽的带限值噪声信号。

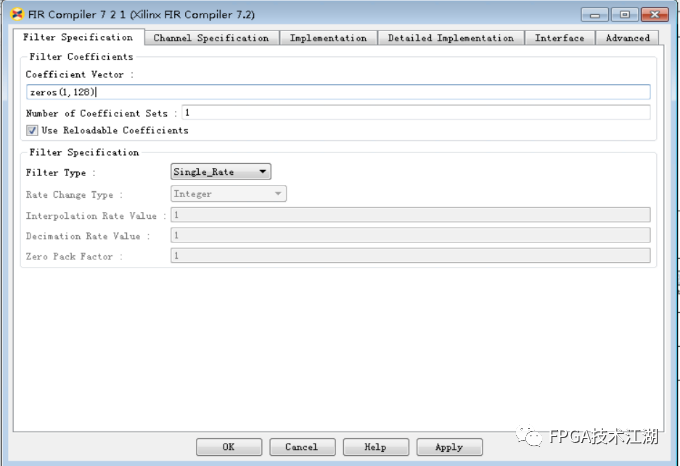

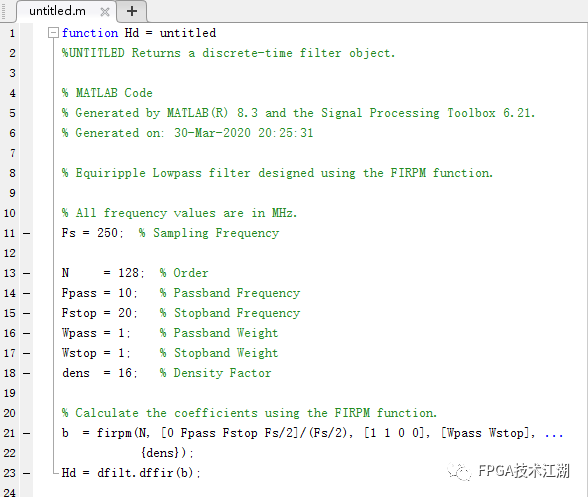

当使用可重新加载的滤波器系数时,内部系数需要设置为相同长度的0,然后使用FDATOOLS设计和推导滤波器系数。

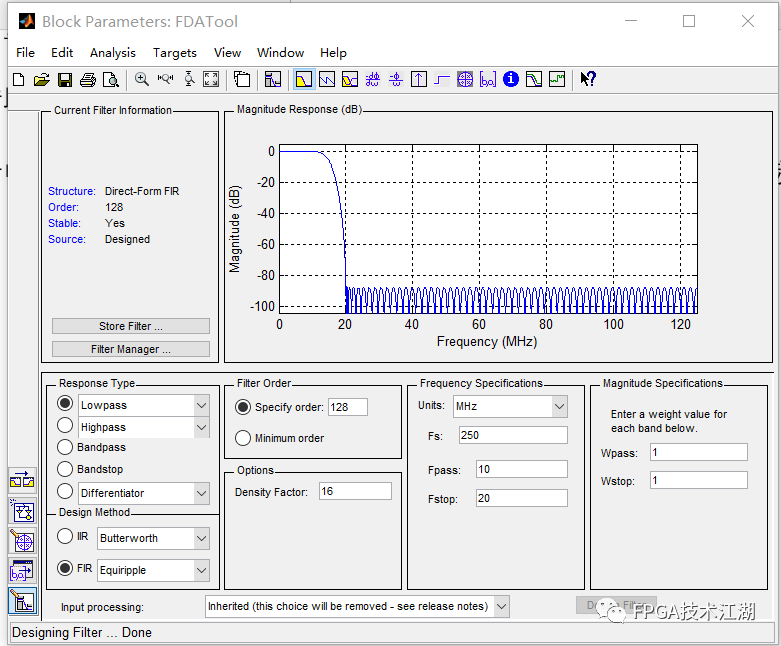

该设计使用低通fir滤波器设计第128阶,250m采样率,PassBand频率为10m和截止频率20m。

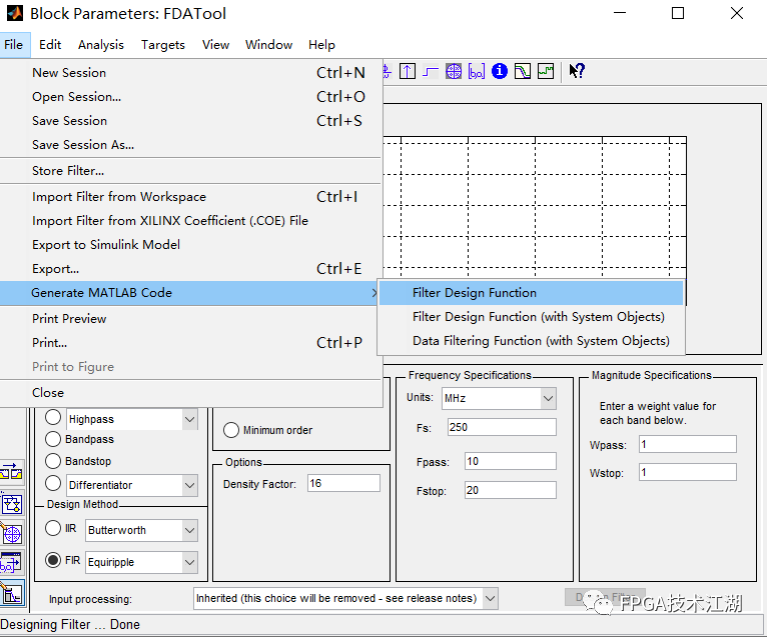

设计完成后,可以通过下面的操作生成系数以生成.m文件,然后可以将其作为重新加载系数输入到过滤器中。

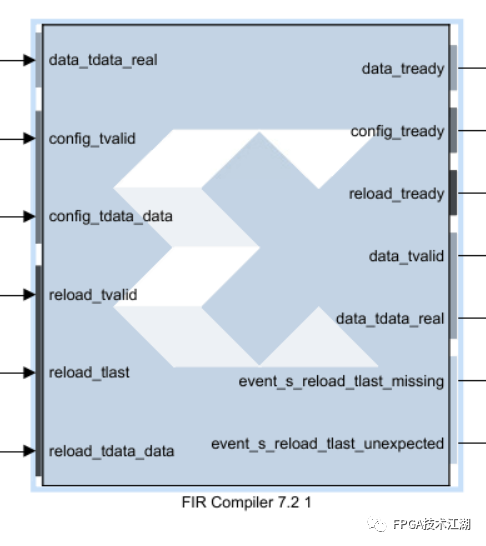

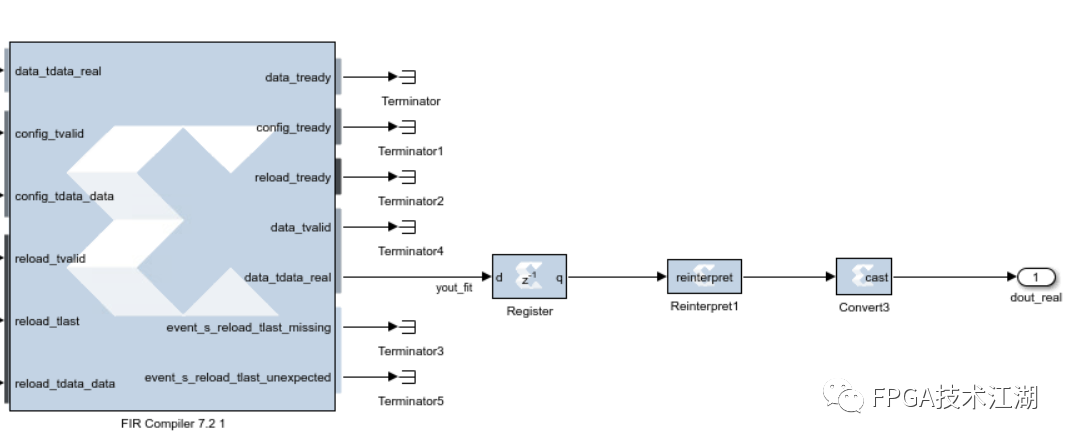

当将过滤器设置为系数重新加载模式时,下图显示了要控制的接口。

其中data_tdata_real是输入数据,而reload_tdata_data是输入系数。

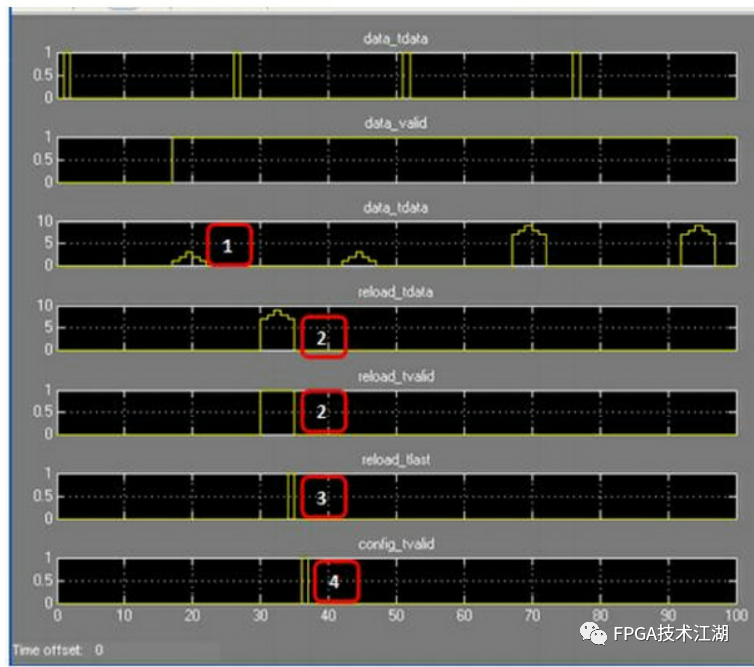

界面的时间表如下图所示:

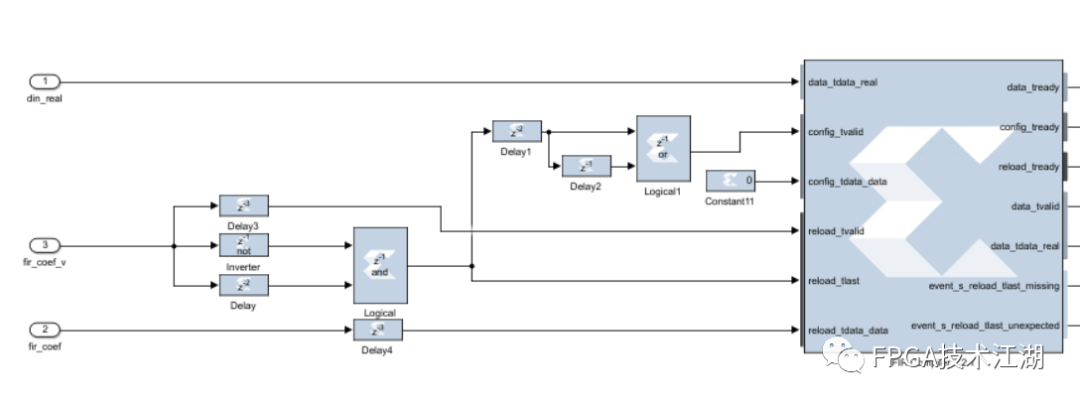

根据计时要求配置FIR过滤器:

然后调整输出数据的位宽度和类型以获得结果。

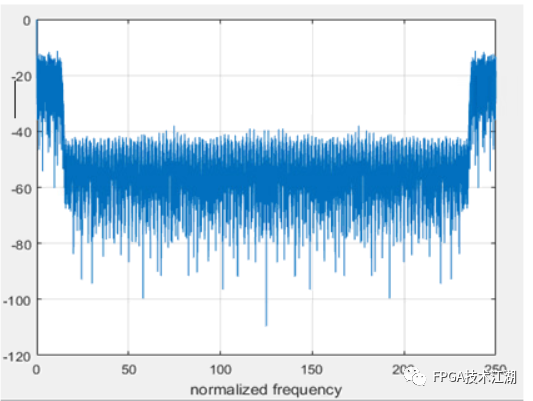

带限制的美白噪声的最终带宽为10m:

这就是今天的全部。将来我将继续与英雄分享。欢迎遵循美丽的“ 1982年计划”。世界是如此大,继续探索kaiyun.ccm,来吧!

- 结束 -

先前的选择

FPGA技术已广泛发表在江户

从初学者到行业精英行业领导者云开·全站体育app登录,从军事行业领域到平民企业开yun体育app官网网页登录入口,从通讯,图像处理到人工智能等,QQ微志者双重选择,FPGA技术世界,从初学者到行业精英行业领导者,从初学者到行业精英行业领导者,从初学者到行业精英行业领导者,从初学者到行业精英行业领导者,FPGA创建最纯粹,最专业的技术交流和学习平台。

FPGA技术Jianghu微信交换集团

加入微信上的小组所有者,请注意名称 + School/Company + Major/Post加入小组

FPGA技术jianghu QQ通信小组

注意名称 +学校/公司 +专业/邮政加入小组