连接/参考器件

AD9139

单通道、1.6 GSPS、16位、TxDAC®数模转换器

ADL5375

宽带正交调制器

AD9516-1

14路输出时钟发生器,集成2.5 GHz VCO

评估和设计支持

电路评估板

该评估板型号为AD9139/ADL5375,具体为AD9139-DUAL-EBZ版本。

数字模式发生器评估板(AD-DPG3)

设计和集成文件

原理图、布局文件、物料清单、软件

电路功能与优势

图1中展示的电路具备同步宽频带发射器的功能,能够适应高达1150 MHz的超宽I/Q带宽。这一设计充分展现了其优异的带内信号性能,包括高无杂散动态范围(SFDR)、低误差矢量幅度(EVM)以及宽频带范围内的平坦频率响应。

在象限误差校正(QEC)过程中,多个通道之间的同步表现至关重要。一旦开启多芯片同步功能,转换器间的延迟差异可能会在单个时钟周期内显现,同时确保同步时钟的精准对齐。

面对高速同步的挑战,关键在于确保数模转换器(DAC)的时钟周期在过程、电压和温度(PVT)条件下达到精确度。为实现这一精确度,必须对DAC实施同步逻辑模块,并且要在电路板上精心规划布局和时钟策略,以确保与同步逻辑模块的协同工作。

该电路适用于E频段的宽带点对点通信,既能保证零中频(ZIF)又能实现复中频(CIF)。其卓越的同步性能,满足了雷达等应用中对严格对齐的严格要求。

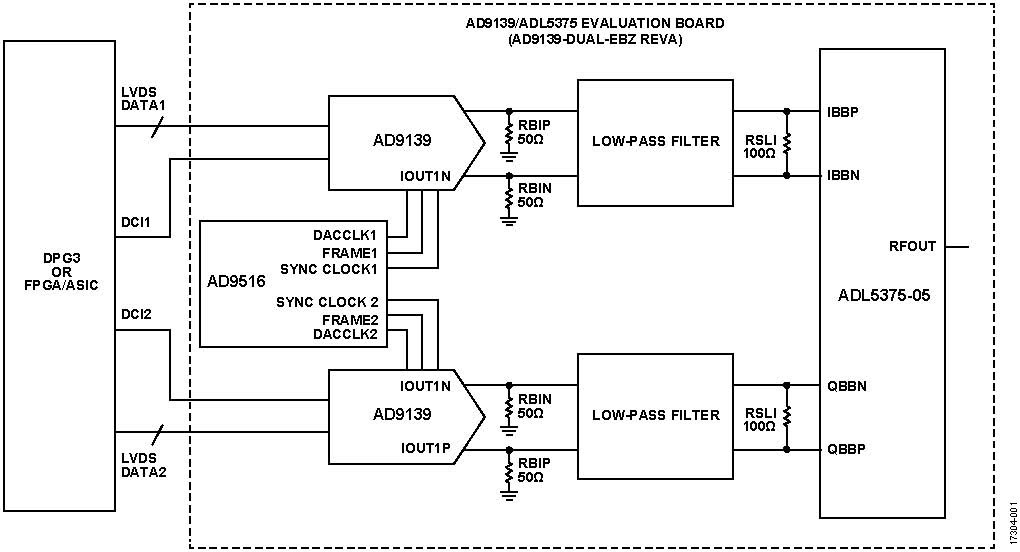

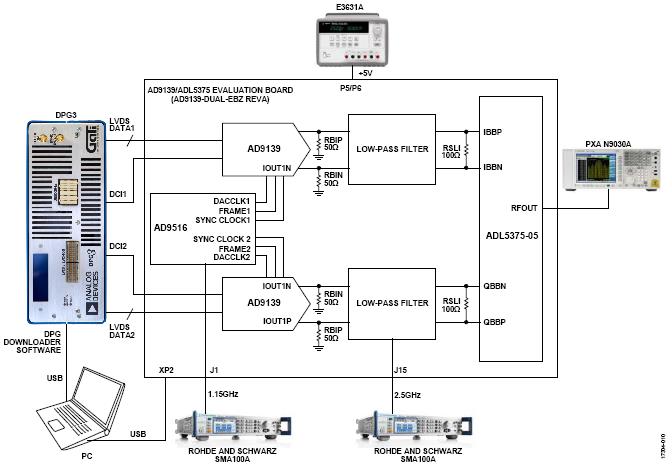

图1.AD9139-DUAL-EBZ评估板功能框图

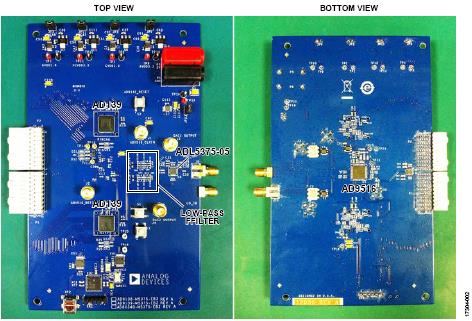

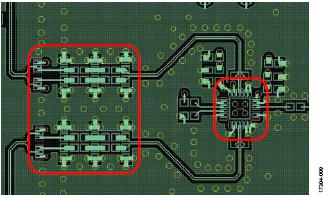

图2.用于实现电路的AD9139-DUAL-EBZ评估板

电路描述

图2展示的电路板上配备了双通道的AD9139 TxDAC单通道转换器、ADL5375-05型号的宽带正交调制器以及AD9516-1型号的时钟发生器。

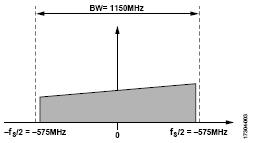

AD9139的数据时钟输入(DCI)的频率上限达到了575 MHz。在此频率下,由于上升沿和下降沿捕捉到的数据都输入到了同一个DAC,因此在1×模式下,数据传输速率可以达到1150 MSPS。为了生成正交数据,我们采用了两个AD9139芯片。每个通道的模拟输出都各自通过一个低通滤波器进行处理。因此,该参考设计能够实现高达1150 MHz的复合带宽,如图3所示。在此宽广的频段内,平坦度显得尤为关键。鉴于AD9139内置了一个能够抵消DAC内部sinc滚降效应的反sinc滤波器kaiyun.ccm,DAC输出后的滤波器平坦度对于整体平坦度的影响变得极为重要。特别是对于并行低电压差分信号(LVDS)接口而言,575 MHz的DDR时钟频率相当高。需要仔细设计LVDS接口的时序。

图3.双AD9139器件的最大带宽

正交调制器

ADL5375-05是一款宽带正交调制器,其输出频率覆盖了从400 MHz到6 GHz的广阔范围。该型号的调制器与AD9139进行I/Q调制时,同样具备400 MHz至6 GHz的宽频率特性。AD9139的输出端与ADL5375-05的输入端采用相同的0.5 V共模电平。

时钟产生和考虑事项

为确保同步的准确性,两个AD9139芯片的DAC时钟、同步时钟以及帧时钟均需精确对齐。AD9516-1具备所需的时钟分配能力,还集成了用于生成更高频率的压控振荡器(VCO)和锁相环(PLL)。在VCO和PLL被禁用,且AD9516-1处于时钟分配模式的情况下,更优的时钟相位噪声有助于实现高速的时钟对齐。当作为时钟分配模式应用时,该设备在1 GHz的输出频率下,分频系数为1,在10 MHz的频率偏移点,其加性相位噪声达到了147 dBc/Hz的水平。Rohde & Schwartz生产的SMA100A型号设备,在相位噪声性能方面表现出色。当它被用作AD9516-1型号设备的输入源时,AD9516-1的输出端总相位噪声几乎触及了时钟分配模式下的最小限制值。

AD9139的多芯片同步

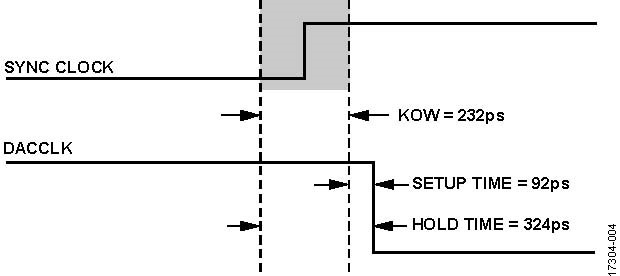

QEC对双通道同步要求极高。DACCLK与同步时钟的布局必须保持对称性。同时,DACCLK与同步时钟的相位应避免位于建立和保持时间窗口内,即应位于该窗口之外。

同步机制确保了在数字模拟转换器(DAC)的输出端kaiyun全站网页版登录,多个通道间在电源电压温度(PVT)变化下的不一致性小于一个DAC时钟周期。以下是用于提升测试性能的操作步骤:

DACCLK 1与DACCLK 2在AD9139的引脚处需确保对齐精准。若DACCLK 1与DACCLK 2之间出现不协调,此不协调将累加至输出端的最终不协调之中。

同步时钟1与同步时钟2需确保精准对齐,同时,它们应分别被DACCLK1和DACCLK2进行采样,以此作为基准。

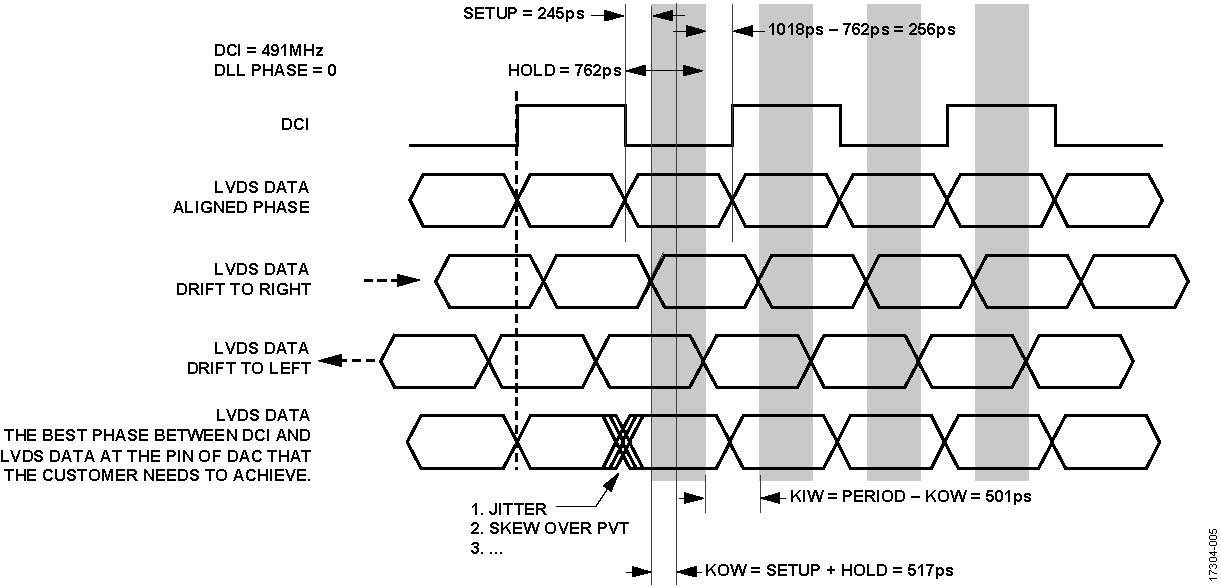

DACCLK与同步时钟的相对相位不能位于KOW范围内,具体如图4所展示。

图4.DACCLK和同步时钟之间的时序要求

LVDS接口设计

当DCI频率达到575 MHz时,在PVT环境中设计LVDS接口往往面临较大困难。本节将通过具体案例来阐述如何进行该接口的设计与优化。

以图5为参照,其DCI频率为491 MHz。依据AD9139的数据手册中的技术规范,若DCI与DATA的边缘在AD9139的引脚处保持良好对齐,那么在延迟锁相环(DLL)的相位被调整为零的情况下,KOW(即设置时间与保持时间的总和)可以被放置在有效窗口的正中央。

数据有效裕量由如下公式定义。

TDATA的有效边限等于TDATA周期减去TDATA偏斜、TDATA抖动以及(阈值加设置时间)的总和。

在整个过程中,无论是变化、电压还是温度,TDATA VALID MARGIN的值都必须大于零,这样才能确保数据的准确采集。

当数字频率指示器显示为491兆赫兹(参见图5),

DCI = 491 MHz(见图5)时,

TDATA PERIOD = 1018 ps

THOLD + TSETUP = 517 ps

在PVT测试中,TDATA SKEW与TDATA JITTER的值必须控制在501 ps以下,这一标准是由用户提出的。其中,TDATA SKEW涵盖了LVDS数据总线延迟的不匹配、PVT过程中DCI与DATA总线间的偏斜等问题。

要优化接口设计,用户可执行以下操作:

在印刷电路板(PCB)上用尽可能短的相同长度的走线。

通过确保以下各项,优化现场可编程门阵列(PFGA):

DCI和DATA的边缘在AD9139的引脚上对齐良好。

在温度和电压变化时,DCI和DATA之间的漂移越小越好。

DCI和DATA之间的抖动越小越好。

在完成DLL相位的扫描之后,AD9139的样本错误检测(SED)功能同样适用于对DCI与DATA之间的时间顺序进行验证。

图5.LVDS时序要求

低通滤波器设计

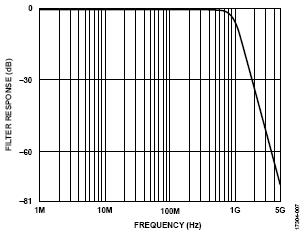

为了实验需求,确保AD9139的性能不受滤波器影响,我们在电路板上特别设计了一个滤波器,该滤波器在240MHz频段内表现出优异的平坦度和群延迟特性。在后续的产品开发过程中,我们能够通过提升滤波器的阶数来进一步提高带外信号的抑制效果。

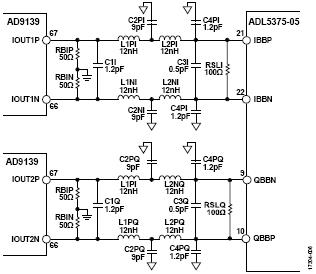

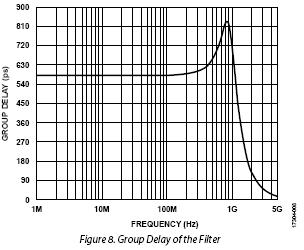

图6中展示的滤波器拓扑结构为五阶巴特沃兹类型,其转折频率设定为900 MHz。相应的仿真响应曲线可参见图7。该滤波器的仿真平坦度在直流至240 MHz的范围内达到了±0.1 dB。此外,其仿真群延迟曲线同样在图7中呈现。

图6展示了推荐的DAC调制器接口的拓扑结构,其中工作频率为900 MHz,并采用了五阶巴特沃兹滤波器。

图7展示了DAC调制器与900 MHz五阶巴特沃兹滤波器相连后的频率响应情况(模拟形式)。

图8.滤波器的群延迟

布局建议

在处理AD9139与ADL5375的接口布局时,需特别留意。以下是一些建议,有助于提升噪声和杂散性能。图9展示了一张依据这些建议设计的顶层布局图。

将DAC、滤波器和调制器放在PCB的同一侧。

收紧滤波器布局:减少L和C的禁区裕量。

将对地电容分三路接到GND平面。

缩短DAC到调制器的距离。

使所有I/Q差分走线长度保持良好的匹配。

滤波器端接电阻尽可能靠近调制器输入端放置。

DAC输出50 Ω电阻尽可能靠近DAC放置。

L和C使用0402封装。

加宽经过滤波器网络的走线以降低信号损耗。

在DAC输出走线区域、滤波器网络周边、调制器输出走线以及LO输入走线邻近,均需布置通孔。

将本振(LO)与调制器输出走线分别布置在独立的层面,或者确保它们之间形成90°的夹角,以此避免相互之间的干扰。

图9.一般布局建议

请访问网站www.analog.com/CN0432-DesignSupport以获取设计支持资料包,同时,您可以在附带的AD9139-DUAL-EBZ布局文件中查阅更多关于正确布局的详细信息。

电路评估与测试

本节内容将详细介绍评估板的配置与检验方法。这些操作流程涵盖了确保评估板正常运作及产生预期效果所必需的基本步骤。如需获取更详尽的资料,请参考AD9139-DUAL-EBZ评估板的快速入门手册。

需要的设备

需要使用以下硬件:

AD9139-DUAL-EBZ

AD-DPG3

Agilent E3631A电源(或同等电源)

频谱分析仪PXA N9030A

Rohde & Schwartz SMA100A信号发生器

带USB端口的PC

USB电缆

需要使用以下软件:

DPG downloader

ACE软件

测试设置

本节将详细阐述采用64 QAM数字调制技术对邻道功率(ACP)和调制误差率(MER)性能的测量方法。测试配置具有灵活性开yun体育app官网网页登录入口,并支持进行其他类型的测量。具体测试配置如图10所示。AD9139-DUAL-EBZ评估板的硬件设备、SPI软件、快速入门指南(QSG)以及DPG3的硬件和软件相关资料均已对外公布。

以Keysight E3631设备为P5/P6电路板供电,电压设定为5伏。同时,利用R&S SMA100A设备为AD9516-1模块提供输入时钟信号。此外,另一个R&S SMA100A设备则负责向ADL5375-05模块输送LO时钟。至于AD9139模块,它将通过串行外设接口(SPI)进行软件编程操作。DPGDownloader软件在PC端运行,负责生成AD9139的发射矢量,并将其下载到DPG3设备中。同时,ADL5375-05的输出信号被接入到Keysight PXA N9030A设备。

图10.测试设置功能框图

测量结果

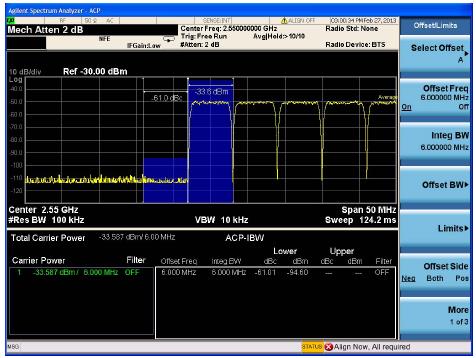

图11展示了ACP测量结果,其最低频率为2.5 G,带宽为6乘以80 MHz,总计达到480 MHz(对应CIF标准)。

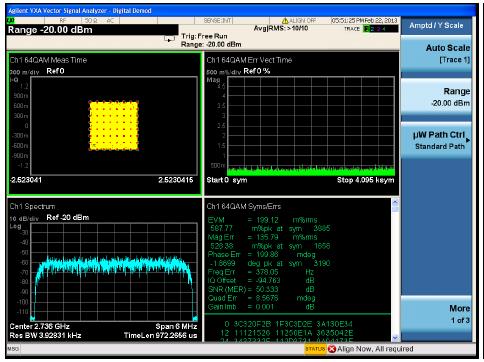

图12展示了MER/EVM的测量结果,其中LO频率设定为2.5 GHz,带宽为6乘以80 MHz,总计达到480 MHz(对应CIF标准)。