随着FPGA技术的不断进步,数字通信领域与FPGA的融合成为现代数字通信系统发展的一大趋势。为了实现高速通信系统的紧凑性、降低成本、减少能耗,尤其是提升设备可靠性,QPSK数字调制技术被广泛应用。该技术具备高频谱利用率、优良频谱特性、强大的抗干扰能力和快速的传输速率等显著优势。采用Verilog语言编写的QPSK调制解调代码,结合Xilinx公司FPGA平台及ISE自带的IP Core进行测试,实验数据表明,该系统不仅成功实现了调制解调的全部功能,而且展现出集成度高的特点,同时支持软件升级等优势。

四相绝对移相键控技术凭借其卓越的抗干扰能力、优异的误码性能以及高效的频谱利用率,在数字通信系统中得到了广泛的应用。伴随着超大规模集成电路的问世,FPGA在数字通信领域的应用范围不断扩大,目前已有多种基于FPGA实现QPSK的技术方案被提出。本篇文章以FPGA为平台,实现了直接数字频率合成技术(DDS),通过调整DDS输出的载波信号相位来达到调相的目的。除了数据转换器(DA转换)之外,整个过程中其余环节均可在FPGA上完成。QPSK调制信号中,载波被抑制,因此不能通过普通的锁相环或窄带滤波器直接获取参考载波。然而,这种信号与某些连续相位调制信号不同,其载波相位的变化仅限于少数几个离散值,这一特性实际上蕴含了参考载波的相位信息。因此,我们可以运用非线性处理手段,去除信号中的调制成分,从而得到与原始载波相位相关的部分,接着对信号进行纯化处理,恢复被抑制的载波信号,最终实现信号的相干解调。本研究提出的QPSK调制解调器,凭借其高效的频带利用率和紧凑的体积、低功耗、高集成度、良好的软件移植性以及强大的抗干扰能力,完全契合了未来通信技术发展的趋势。

1.QPSK调制的基本原理

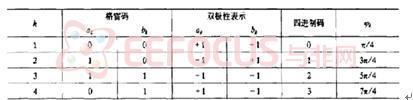

四相绝对移相键控QPSK属于MPSK的特定形态,这种技术通过四种不同的载波相位来表示数字信号。因为每个载波相位可以代表两个比特的数据,所以四进制码元也被称作双比特码元。在双比特码元中云开·全站体育app登录,我们将前面的信息比特记为a,而后面的比特信息则用b来表示。在双比特码元中,两个信息比特ab一般遵循格雷码(亦称反射码)的顺序排列。若ab组合为00,则对应的载波相位为0度;若ab组合为01,载波相位则为90度;若ab组合为11,载波相位将变为180度;而若ab组合为10,载波相位将达到270度。

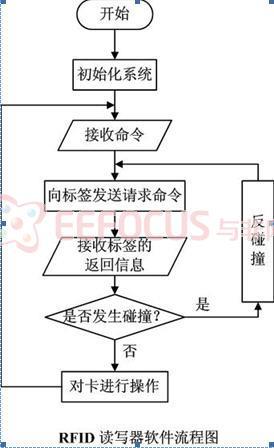

QPSK信号的生成途径包括调相技术与相位挑选技术。鉴于调相技术更为普遍且操作简便,本文采纳了此方法。QPSK信号通过调相法生成的系统框图详见图1。在该图中,串行/并行转换器将输入的二进制数据流逐一拆分为两个并行的双极性数据流。设这两个数据流中的二进制位分别为a与b,每一对a和b组合构成一个双比特符号。a和b两种极性脉冲分别被送入两个平衡调制器,这些调制器随后对同相载波和正交载波实施二相调制操作。将ab两路信号相加,从而产生四相移相信号,其相位编码遵循以下逻辑:若双比特码元ab为11,则输出315°的载波信号;若ab为01,则输出225°的载波信号;若ab为00,则输出135°的载波信号;若ab为10,则输出45°的载波信号。具体对照关系可参考下表。

此宽度设定为620像素,样式设置为鼠标悬停时指针变为手指图标,点击可执行相应操作。

数据与相位的对照关系

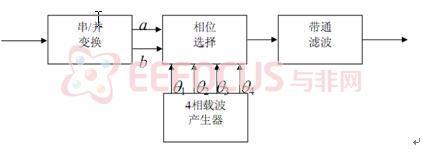

传统的QPSK模拟调制器设计多采用正交调制技术。在全数字调制器的构建中,正交调制方法依旧被运用,但模拟处理环节已被数字信号处理算法所取代。QPSK技术通过四种不同的载波相位来编码数字信息,其中每个相位对应2比特数据。其实现途径包括相位选择法和正交调制法,而相位选择法又细分为A型和B型两种具体方式。本文采用相位选择法B方式来实现QPSK信号,如图1所示。

620)this.width=620;" style="cursor:pointer" />

图1 QPSK调制框图

2.QPSK调制的MATLAB仿真

关于QPSK调制的MATLAB仿真,网络上资源丰富,作者独立编写了相应的代码,用以直观展示调制的基本原理。以下列出该代码,其注释详尽,无需过多解释。读者需将代码与解调部分综合研读。

clear all;

clc

M=4;

Ts=1;

fc=5;

N_sample=8;%每个正弦波采样点数

N_num=300;%I Q路分别100个bit

dt=1/fc/N_sample;

t=0:dt:N_num*Ts-dt;

T=dt*length(t);

噪声值等于(1除以500)乘以从randn函数生成的(1,length(t))维度的随机数,再乘以32767,以此方式添加至信号中。

py1f=zeros(1,length(t));

py2f=zeros(1,length(t));

for PL=1:1:700%加入噪声强度加大

d1=sign(randn(1,N_num));

d2=sign(randn(1,N_num));

d=;

D=reshape(d,1,);%D是输入的信息序列

gt=ones(1,fc*N_sample);

此操作是对d1进行符号位扩展,扩展后的结果赋值给s1,其中扩展的次数为fc乘以N_sample,具体的相关函数实现可以在原始代码中找到。

s2=sigexpand(d2,fc*N_sample);

b1=conv(s1,gt);

b2=conv(s2,gt);

s1=b1(1:length(s1));

s2=b2(1:length(s2));

将经过定点量化的数据分为两部分,即st_qpsk_1和st_qpsk_2,然后将它们相加,得到最终的st_qpsk值。

坚决杜绝任何对专业知识的篡改,确保学术研究的严谨性,维护学术界的纯洁度,坚守学术道德底线。

% 发射信号的功率谱

绘制图形,展示对st_qpsk信号进行2048点快速傅里叶变换(FFT)后,取绝对值并平方的结果。

3.QPSK调制的FPGA实现

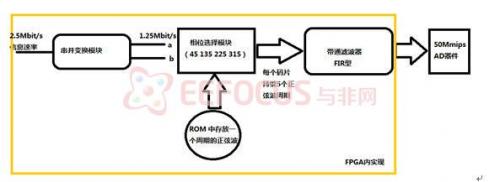

图2展示了QPSK的FPGA设计内部逻辑,其最高传输速率可达2.5Mbit/s。设计流程中,信息速率先由串并变换模块降低至1.25Mbit/s,接着通过相位选择模块,从45度、135度、225度和315度相角中选取一个作为正弦波的起始相位。每个码片持续5个正弦波周期,但码片起始和结束时的相位差异会导致输出信号频谱出现严重混叠,这给后续处理带来不便。因此,在输出端口加入了FIR型带通滤波器,以使带外信号迅速衰减至极低水平。

该信号经过模数转换器处理,转变为模拟形式开yun体育app官网网页登录入口,随后便能够传输至后续的相应芯片进行进一步处理,具体过程本文将不予详细阐述。

620)this.width=620;" style="cursor:pointer" />

图2 系统框图

调制代码文件之间的逻辑关系入下图所示:

620)this.width=620;" style="cursor:pointer" />

各个文件的逻辑关系

QPSK_CODING.V文件位于调制流程的最顶端,该文件的对外接口信息如下所示,

定义模块QPSK_CODING,其中包含输入参数clk_2_5M、clk_50M、clk_1_25M、EN、din、ready,以及输出参数dataout和count;

接收时钟信号clk_2_5M、clk_50M、clk_1_25M、使能信号EN以及数据输入din。

output ready;

output dataout;

output count;

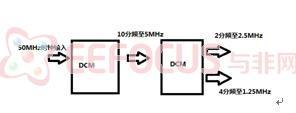

本方案采用了三种时钟,它们之间的相互联系如下所述,在硬件的实际构建中,需要由两个DCM模块构成。

620)this.width=620;" style="cursor:pointer" />

数字时钟管理单元

620)this.width=620;" style="cursor:pointer" />

各时钟之间的关系图

图中展示的模拟情景是建立在将14比特数据输入至该调制装置的基础之上,经过调制过程,最终输出的结果呈现如下情形:

620)this.width=620;" style="cursor:pointer" />

经过调制后的QPSK信号波形图(未加滤波器前的输出)

改设计的其他相关模块的设计上层逻辑模块如下所示:

数据流首先被输入到串并变换模块,该模块名为serial_to_parallel,随后,它接收时钟信号clk_2_5M、使能信号EN、数据输入din以及就绪信号ready,最终输出转换后的数据dataout。

接着,我们需执行模块“module Produce_Sin(EN,clk_2_5M,clk_50M,datain,ready,addr,count)”的生成过程;该模块接受多个输入参数,包括EN、clk_2_5M、clk_50M、datain、ready、addr和count。

4.QPSK解调的基本原理

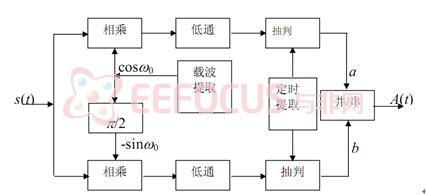

在全数字化的QPSK解调流程中,AD接口前端部分对处理速度的要求极高;然而,所涉及的算法却相对简便;FPGA器件具备的并行实时处理能力恰好适用于这一环节;鉴于此,从ADC输出的数字信号处理任务便完全交由FPGA来完成。鉴于QPSK的相干检测相较于差分检测能够带来2.3dB的功率提升,因此我们决定采用相干解调算法来进行信号解调。具体的解调流程框图,请参考图2。

本论文所采纳的解调策略涉及将A/D转换后得到的数字信号x(n)与由NCO生成的两个相互垂直的本地载波进行乘法运算,接着,这些信号分别通过低通滤波器进行滤波处理,从而获得基带信号。从这些基带信号中,我们提取出同步信息,并利用载波同步模块对NCO的输出进行相应的调整。最终,经过解差分与并串转换,我们得到了调制信息。

620)this.width=620;" style="cursor:pointer" />

图2 QPSK解调框图

图中所示,载波恢复电路首先从接收到的QPSK信号中提取出与原始传输载波频率和相位一致的载波振荡信号。接着,该电路将接收到的QPSK信号分为两路,其中一路与恢复的载波直接相乘,另一路则与相位偏移90°的恢复载波相乘。随后,这两个乘积项分别进行积分处理,恢复的位时钟对积分结果进行抽样。最后,通过判决过程再生出原始的I、Q数据比特,并由并、串变换器将并行的I、Q数据转换为串行二进制输出数据。

卡斯特环法提取载波的一个方法入下图所示:

620)this.width=620;" style="cursor:pointer" />

卡斯特环法提取载波原理图

5.QPSK解调的MATLAB仿真

此代码上接QPSK调制代码,

严禁对特定内容进行篡改kaiyun全站网页版登录,确保信息的准确性和完整性,同时维护知识体系的权威性。

% 信道传输

st_qpsk更新为:st_qpsk等于原st_qpsk加上噪声乘以功率水平减一的值。

st_qpsk经过四舍五入处理,等于其最大绝对值除以自身最大绝对值再乘以32767的结果;这是AD采样后的数据,采用16比特表示。

%----------------------------------------------------

% 解调 将32位宽截取到16位

decode_qpsk_s1等于将(st_qpsk乘以round(cos(2*pi*fc*t)*32767))的结果四舍五入,然后除以2的16次方。

decode_qpsk_s2等于对st_qpsk进行取整操作,取整的依据是对(2*pi*fc*t)乘以sin函数的结果,该结果先乘以32767,然后除以2的16次方,最终得到的值也进行取整处理。

不得擅自更改专业术语,确保表述准确无误,同时遵守相关规定。

% 定点FIR滤波器

Num_fix=

一亿零六十七万二千七百四十五万一千零二十四,一千零二十四,七百四十五万三千七百二十六,一百零六。

Num_fix_2=

在1号、8号、23号、55号、109号、189号、298号、431号、581号、732号、867号、969号、1024号、1024号、969号、867号、732号、581号、431号、298号、189号、109号、55号、23号、8号和1号这些日期上,均不得进行修改。

对fir_output_s1进行四舍五入处理,结果为原值除以1024,并保留整数部分。

在第一个子图区域中,绘制了时间序列t与滤波器输出s1的图像;使用subplot函数将绘图区域分为2行1列,并选中第一个子图进行绘制。

对fir_output_s2进行四舍五入处理,结果等于其自身除以1024,然后取整;即,执行截取操作。

在2行1列的子图布局中,选取第2个子图;绘制时间序列t与滤波器输出s2之间的关系图。

严禁对特定内容进行篡改,确保信息的真实性,维护学术研究的严谨性。

% 判决decode_s1 decode_s2

从20开始,以(N_num乘以N_sample再乘以fc)为步长,循环至40。

if(fir_output_s1(k)>0)

decode_s1(round((k)/40))=1;

else

decode_s1(round((k)/40))=-1;